“微电子光电子器件的高性能封装原理、新工艺与装备”研究进展

发布时间:2018-04-19 浏览次数:

微电子和光电子是信息技术的两大支柱。我国微电子封装产业达到数千亿元。互连封装占微电子、光电子器件制造成本的70%以上。

为了自主研发新一代微电子光电子器件的互连封装技术,项目组深入研究封装机理,提出新工艺,自主研发高性能封装装备。主要成果有:

(1)微电子互连封装:揭示了三维引线成形机理,提出了引线弧线的圆心映射快速设计新方法,自主研发了长引线低弧度高密度金丝球焊方法、多芯片堆叠互连技术、厚膜悬臂键合新工艺,研制了压电驱动胶液精确喷射阀。

(2)光电子耦合封装:建立了光电子器件的耦合传输分析模型,提出了自动耦合封装工艺和全局寻优搜索算法,自主研发了多个类型器件的自动化高性能耦合封装装备,打破了国际垄断。

成果广泛应用于我国微电子光电子封装企业,有力推动了行业技术发展。

随着微电子互连向高密度、超薄及凸点间距缩小发展,多芯片叠层和悬臂结构使三维封装易产生键合过程失效、超低弧(<75μm)、大跨距(6-8mm)引线稳定性等问题,对引线互连技术提出了新挑战。

(1)提出了引线弧线的圆心映射设计新方法,建立了复杂引线成形设计模型

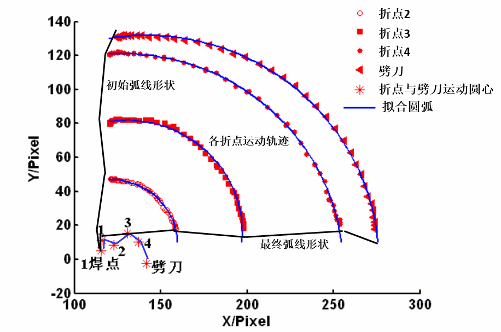

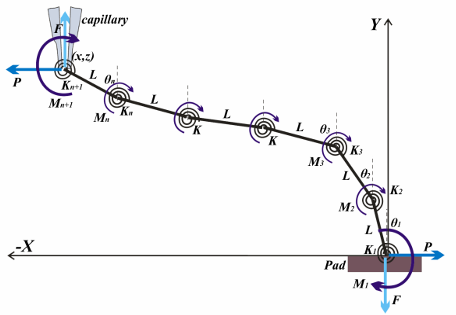

揭示了引线的成形机制和刚度规律,提出了基于圆心映射的劈刀路径规划与弧线设计新方法;建立了引线弧形的可变长连杆-弹簧设计模型,开发了设计软件,实现了复杂形状低弧大跨度 (折点≥5个、跨度>8000μm、弧高<120μm) 引线的快速、准确设计,打破了国外对弧线设计技术的垄断。

基于圆心映射的通用弧线设计方法 可变长连杆-弹簧(VLLS)分析设计模型

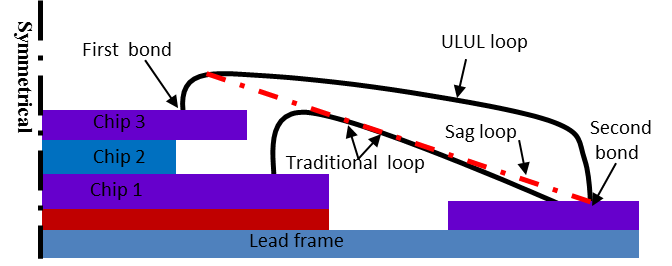

针对三维封装技术需求,开发了深腔键合新引线工艺;提出了三维叠层封装的弧线形式,引入支撑点来形成折点,实现了超低超大跨度弧线成形。

深腔键合引线成形过程的可视化设计 三维叠层封装超低超大跨度n弧线

提出了长引线低弧度高密度金丝球焊方法,完成了引脚100个、间距0.4mm、厚度1.4mm的窄间距引线键合;开发了多芯片堆叠三维封装的低弧度压焊技术,解决了低弧度窄间距引线易碰线难题,实现了3层以上堆叠芯片的引线互连。

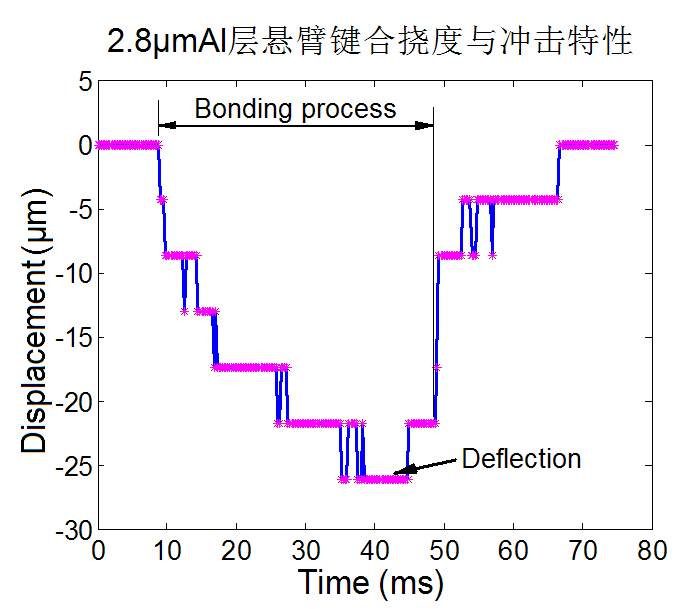

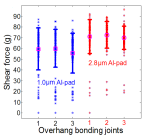

(3)提出了厚膜悬臂键合新工艺,提高了键合强度

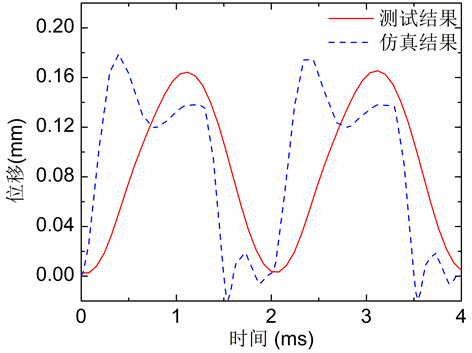

针对Cu线悬臂键合过程冲击大、难以实现高性能键合的问题,提出了增加芯片焊盘的Al层厚度、改善动力学特性、减小冲击的工艺思路。将Al层厚度增加到2.8μm,挠度减小了70%,提高了悬臂键合强度。

芯片Al层1.0μm的实时挠度(左),芯片Al层2.8μm的实时挠度(中),剪切强度(右)

(4)提出了用于封装的高速度高精度喷射点胶新技术

揭示了喷射点胶机理,提出了通过放大喷针位移实现高速度高精度喷胶的技术思路,研制了压电驱动的喷射点胶阀,点胶速度达300点/秒,最小胶滴体积25纳升,胶滴直径误差小于10%,部分性能达到国际领先水平。

压电驱动喷射阀 喷射阀控制电路 喷针位移曲线

2、自主研发了同轴型光电子器件的高性能耦合封装工艺与装备

光电子器件耦合封装是将其功能结构与光纤耦合,制造高精度高保真的光信号传输通道。由于单模光纤芯径只有8-10微米,因此其耦合对准是严峻的技术挑战,需要达到亚微米精度,自动化耦合封装技术与装备被国外垄断。

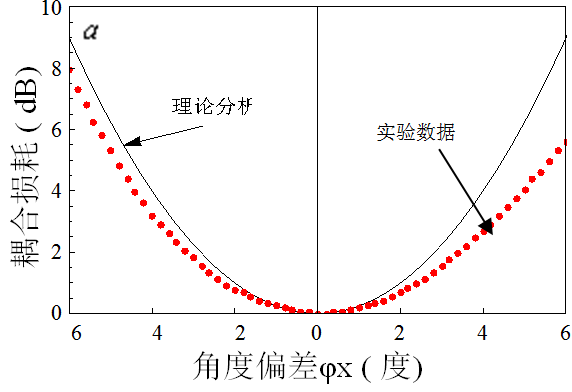

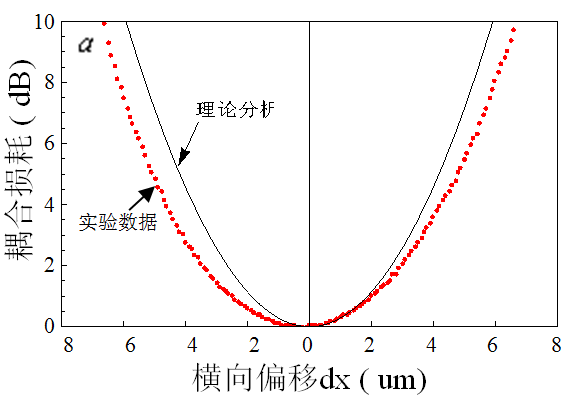

(1)建立了光电子器件耦合传输模型,确定了耦合精度阈值

揭示了耦合界面的光波传输与畸变行为,建立了耦合模型,获得了耦合误差对光传输性能的影响规律,确定了横向偏移量容差为±1μm。

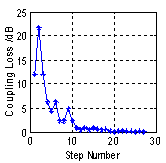

器件耦合的损耗规律

(2)研发了光电子器件的高性能自动耦合封装工艺,提出了全局耦合搜索算法

为了解放封装工人的眼睛,自主研发了自动化耦合封装工艺,提出了基于光学耦合模型的全局耦合搜索算法,开发了快速定量反馈控制系统,克服了人工对准封装对操作员的依赖性,提高了性能一致性和生产效率。

器件耦合过程及其光功率损耗变化

(3)自主研制了多种类型光电子器件的高性能自动化耦合封装设备

突破了自动耦合对准、在线检测、激光焊接等关键技术,自主研制了EPON 、LD、PD等光电子器件的自动化耦合封装设备,耦合对准精度达到0.3 mm,器件封装后功率降<0.5dB,实现了高精度高性能耦合封装,打破了国际垄断。

EPON耦合焊接设备 LD耦合焊接设备 PD耦合粘接设备

3、成果影响与工业应用

发表SCI论文152篇,获得国家授权专利21项,出版专著4本,获省部级一等奖2项、二等奖3项。

自主研发的封装技术与装备打破了国际垄断,成功应用于我国微电子光电子器件封装制造行业,为行业技术发展做出了重要贡献:

(1)微电子三维封装技术应用于我国中电科45所、华天科技等微电子封装企业。压电驱动喷射点胶阀应用于京东方、天马等新一代显示器制造龙头企业。

(2)光电子器件的自动化耦合封装装备广泛应用于深圳九州、青岛海信、武汉正源、育诚飞等10余家光电子企业,有力推动了行业的技术进步。